| Fanout Enabled Structures |

|

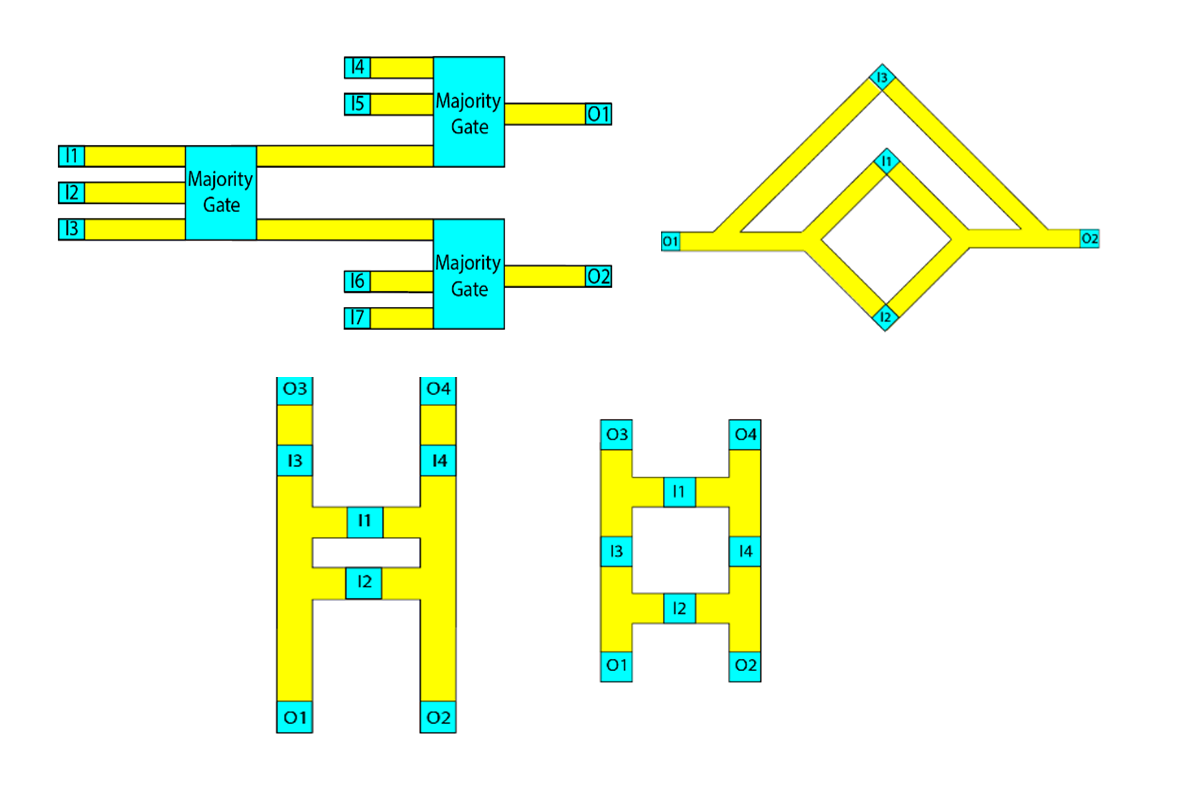

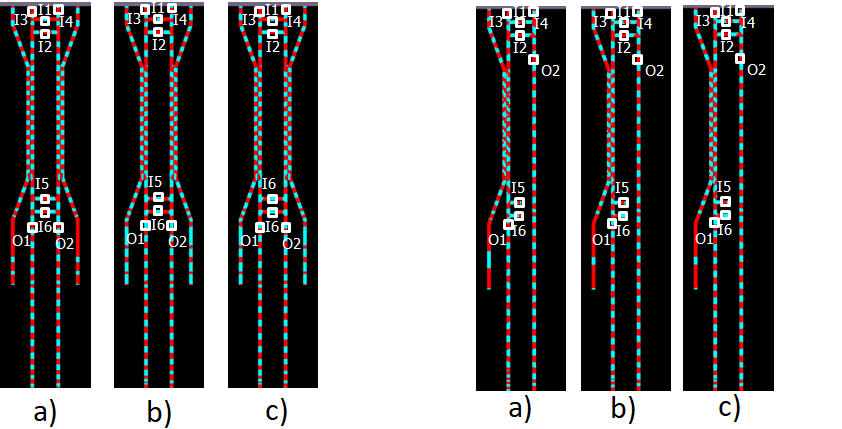

The realization of any circuit requires gate fanout capabilities as one gate output is often utilized as input for more than one gate. Fanout achievement is straightforward in charge-based circuits but it requires wave replication in the SW domain. Theses gates are introduced in [1] [2] [3] [4] and provide fanout values of 2 and 4 within the SW domain. [1] Mahmoud et al., AIP Advances 10, 035119 (2020); [2] Mahmoud et al., 2020 IEEE Computer Society Annual Symposium on VLSI (ISVLSI); [3] Mahmoud et al., 2020 IEEE 38th International Conference on Computer Design (ICCD); |

|

|

|

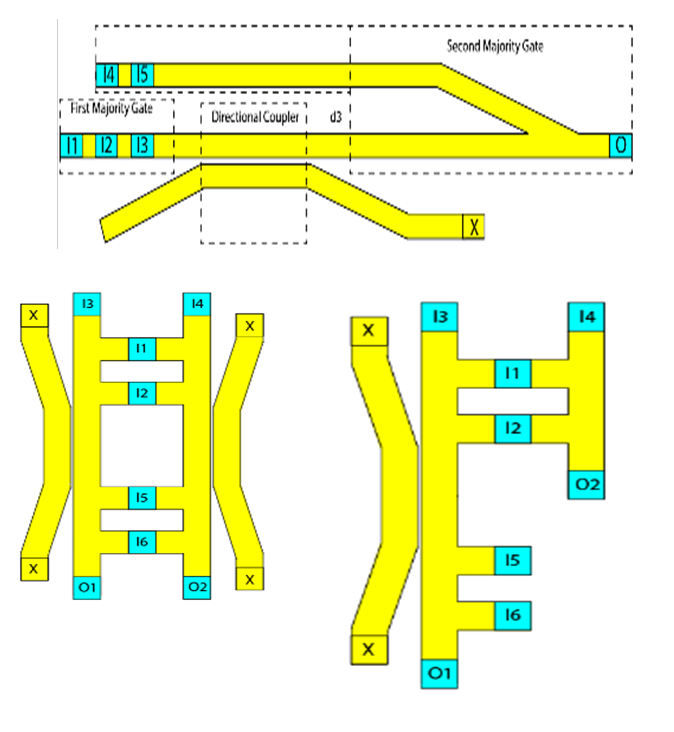

| Different types of Cascaded Majority Gates | |

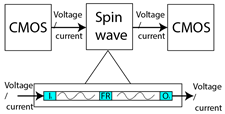

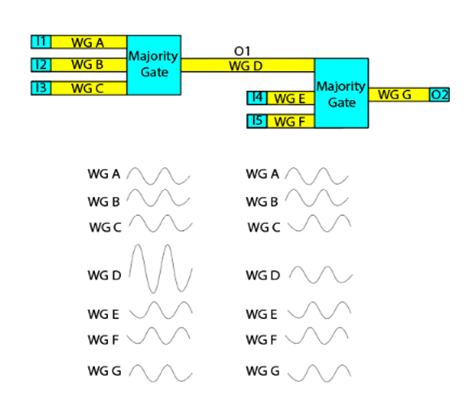

| To create energy effective data processing islands, SW gates have to be interconnectable within the SW domain. By their very nature SW Majority gates are not input-output SW amplitude coherent as indicated in the figure on the left. As such their direct cascading may produce wrong results. One solution is to rely on wave to voltage and back convertors, but this precludes the harvesting of the SW technology low power potential (it is against the hybrid architecture philosophy). | |

|

|

| Top | |

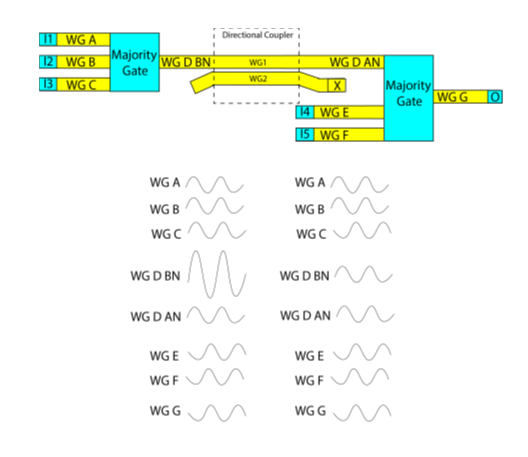

| As shown in the figure on the right, a directional coupler allows for Majority gates cascading within the SW domain (details: Mahmoud et al., IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 1, pp. 536-549, Jan. 2021). | |

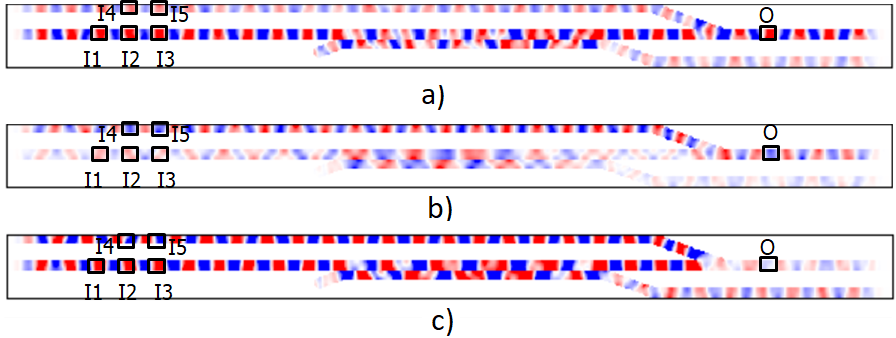

| Proposed Gates Cascading Solution Structures | OOMMF Simulation Results a) I1I2I3I4I5=00000, b) I1I2I3I4I5=00111, c) I1I2I3I4I5=00011 |

|

|

|

|

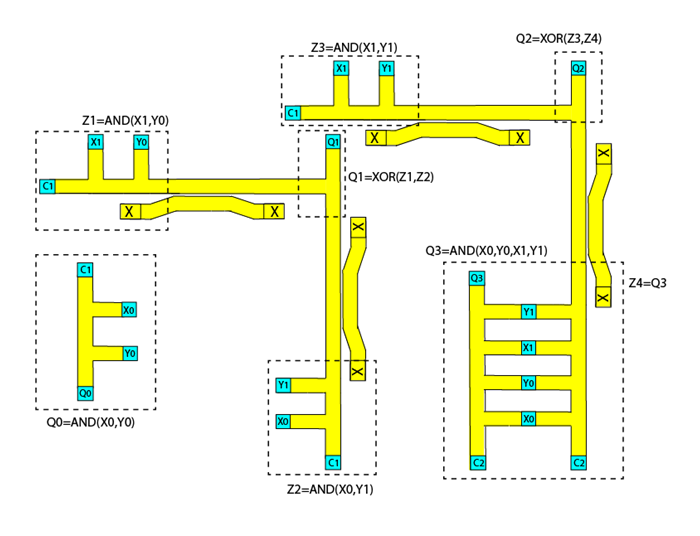

| 2-bit Inputs Spin Wave Multiplier | |

|

SW domain only 2-bit input operand multiplier (X = (X1,X0), Y = (Y1,Y0), |

|

| Top | |